Distributed by:

JAMECO

ELECTRONICS

### www.Jameco.com + 1-800-831-4242

The content and copyrights of the attached material are the property of its owner.

Jameco Part Number 843180

### LMX2306/LMX2316/LMX2326

## PLLatinum™ Low Power Frequency Synthesizer for RF

### **Personal Communications**

LMX2306 550 MHz LMX2316 1.2 GHz LMX2326 2.8 GHz

### **General Description**

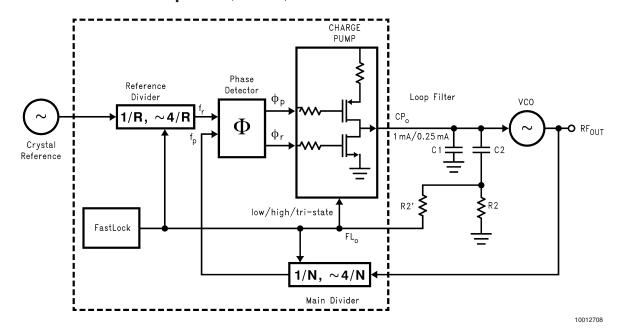

The LMX2306/16/26 are monolithic, integrated frequency synthesizers with prescalers that are designed to be used to generate a very stable low noise signal for controlling the local oscillator of an RF transceiver. They are fabricated using National's ABiC V silicon BiCMOS 0.5µ process.

The LMX2306 contains a 8/9 dual modulus prescaler while the LMX2316 and the LMX2326 have a 32/33 dual modulus prescaler. The LMX2306/16/26 employ a digital phase locked loop technique. When combined with a high quality reference oscillator and loop filter, the LMX2306/16/26 provide the feedback tuning voltage for a voltage controlled oscillator to generate a low phase noise local oscillator signal. Serial data is transferred into the LMX2306/16/26 via a three wire interface (Data, Enable, Clock). Supply voltage can range from 2.3V to 5.5V. The LMX2306/16/26 feature ultra low current consumption; LMX2306 - 1.7 mA at 3V, LMX2316 - 2.5 mA at 3V, and LMX2326 - 4.7 mA at 3V.

The LMX2306/16/26 synthesizers are available in a 16-pin TSSOP surface mount plastic package.

### **Features**

- 2.3V to 5.5V operation

- Ultra low current consumption

- 2.5V V<sub>CC</sub> JEDEC standard compatible

- Programmable or logical power down mode:

- I<sub>CC</sub> = 1  $\mu$ A typical at 3V

- Dual modulus prescaler:

- LMX2306 8/

- LMX2316/26 32/33

- Selectable charge pump TRI-STATE® mode

- Selectable FastLock<sup>™</sup> mode with timeout counter

- MICROWIRE™ Interface

- Digital Lock Detect

### **Applications**

- Portable wireless communications (PCS/PCN, cordless)

- Wireless Local Area Networks (WLANs)

- Cable TV tuners (CATV)

- Pagers

- Other wireless communication systems

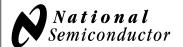

### **Functional Block Diagram**

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

FastLock™, PLLatinum™ and MICROWIRE™ are trademarks of National Semiconductor Corporation.

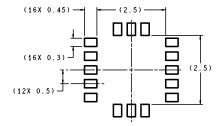

### **Connection Diagrams**

#### LMX2306/16/26 0 $CP_o$ 15 $V_{CC2}$ GND · Fo/LD GND • 13 - LE TOP VIEW $f_{IN}$ 12 **-** Data – Clock $f_{\mathsf{IN}}$ 11 **-** CE 10 $V_{CC1}$ osc<sub>IN</sub> GND

16-Lead (0.173" Wide) Thin Shrink Small Outline

Package(TM)

Order Number LMX2306TM, LMX2306TMX, LMX2316TM,

LMX2316TMX,

LMX2326TM or LMX2326TMX

See NS Package Number MTC16

#### LMX2306/16/26 $FL_{o}$ GND 16 15 14 $V_{CC} 2$ GND 12 $F_o/LD$ Top View LE $\overline{f_{\text{IN}}}$ Data 10 $\mathsf{f}_{\mathsf{IN}}$ V<sub>CC</sub> 1 5 9 Clock $OSC_{in}$ GND

16-pin Chip Scale Package

Order Number LMX2306SLBX, LMX2316SLBX or

LM2326SLBX

See NS Package Number SLB16A

### **Pin Descriptions**

| 16-Pin |     | Pin               | I/O | Description                                                                                                                                                                                                                                                                                            |

|--------|-----|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP  | CSP | Name              |     |                                                                                                                                                                                                                                                                                                        |

| 1      | 15  | $FL_o$            | 0   | FastLock Output. For connection of parallel resistor to the loop filter. (See Section 1.3.4 FASTLOCK MODES description.)                                                                                                                                                                               |

| 2      | 16  | CPo               | 0   | Charge Pump Output. For connection to a loop filter for driving the input of an external VCO.                                                                                                                                                                                                          |

| 3      | 1   | GND               |     | Charge Pump Ground.                                                                                                                                                                                                                                                                                    |

| 4      | 2   | GND               |     | Analog Ground.                                                                                                                                                                                                                                                                                         |

| 5      | 3   | f <sub>IN</sub>   | I   | RF Prescaler Complementary Input. A bypass capacitor should be placed as close as possible to this pin and be connected directly to the ground plane. The complementary input can be left unbypassed, with some degradation in RF sensitivity.                                                         |

| 6      | 4   | $f_{IN}$          | ı   | RF Prescaler Input. Small signal input from the VCO.                                                                                                                                                                                                                                                   |

| 7      | 5   | V <sub>CC1</sub>  |     | Analog Power Supply Voltage Input. Input may range from 2.3V to 5.5V. Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane. $V_{\rm CC1}$ must equal $V_{\rm CC2}$ .                                                                      |

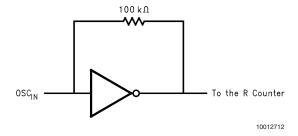

| 8      | 6   | OSC <sub>IN</sub> | I   | Oscillator Input. This input is a CMOS input with a threshold of approximately V <sub>CC</sub> /2 and an                                                                                                                                                                                               |

|        |     |                   |     | equivalent 100k input resistance. The oscillator input is driven from a reference oscillator.                                                                                                                                                                                                          |

| 9      | 7   | GND               |     | Digital Ground.                                                                                                                                                                                                                                                                                        |

| 10     | 8   | CE                | I   | Chip Enable. A LOW on CE powers down the device and will TRI-STATE the charge pump output. Taking CE HIGH will power up the device depending on the status of the power down bit F2. (See Section 1.3.1 POWERDOWN OPERATION and Section 2.1 DEVICE PROGRAMMING AFTER FIRST APPLYING V <sub>CC</sub> .) |

| 11     | 9   | Clock             | I   | High Impedance CMOS Clock Input. Data for the various counters is clocked in on the rising edge into the 21-bit shift register.                                                                                                                                                                        |

| 12     | 10  | Data              | I   | Binary Serial Data Input. Data entered MSB first. The last two bits are the control bits. High impedance CMOS input.                                                                                                                                                                                   |

| 13     | 11  | LE                | I   | Load Enable CMOS Input. When LE goes HIGH, data stored in the shift registers is loaded into one of the 3 appropriate latches (control bit dependent).                                                                                                                                                 |

| 14     | 12  | Fo/LD             | 0   | Multiplexed Output of the RF Programmable or Reference Dividers and Lock Detect. CMOS output. (See <i>Table 4</i> .)                                                                                                                                                                                   |

| 15     | 13  | V <sub>CC2</sub>  |     | Digital Power Supply Voltage Input. Input may range from 2.3V to 5.5V. Bypass capacitors should be placed as close as possible to this pin and be connected directly to the ground plane. $V_{\rm CC1}$ must equal $V_{\rm CC2}$ .                                                                     |

| 16     | 14  | V <sub>P</sub>    |     | Power Supply for Charge Pump. Must be ≥ V <sub>CC</sub> .                                                                                                                                                                                                                                              |

### **Absolute Maximum Ratings** (Notes 1, 2)

| Power Supply Voltage                        |                         |

|---------------------------------------------|-------------------------|

| V <sub>CC1</sub>                            | -0.3V to $+6.5V$        |

| V <sub>CC2</sub>                            | -0.3V to $+6.5V$        |

| $V_p$                                       | -0.3V to $+6.5V$        |

| Voltage on Any Pin                          |                         |

| with $GND = 0V(V_I)$                        | –0.3V to $V_{\rm CC}$ + |

|                                             | 0.3V                    |

| Storage Temperature Range (T <sub>S</sub> ) | −65°C to +150°C         |

| Lead Temperature (T <sub>L</sub> )          |                         |

# **Recommended Operating Conditions**

|                                         | Min           | Max       | Units |

|-----------------------------------------|---------------|-----------|-------|

| Power Supply Voltage                    |               |           |       |

| V <sub>CC1</sub>                        | 2.3           | 5.5       | V     |

| V <sub>CC2</sub>                        | $V_{\rm CC1}$ | $V_{CC1}$ | V     |

| $V_p$                                   | $V_{CC}$      | 5.5       | V     |

| Operating Temperature (T <sub>A</sub> ) | -40           | +85       | °C    |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended operating conditions indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed.

**Note 2:** This device is a high performance RF integrated circuit with an ESD rating < 2 kV and is ESD sensitive. Handling and assembly of this device should only be done at ESD protected work stations.

### **Electrical Characteristics**

(solder, 4 sec.)

$V_{CC}$  = 3.0V,  $V_p$  = 3.0V; -40°C <  $T_A$  < 85°C except as specified

| Symbol                  | Parameter                 |           | Conditions                                                       |                       | Values |                          |     |  |  |

|-------------------------|---------------------------|-----------|------------------------------------------------------------------|-----------------------|--------|--------------------------|-----|--|--|

|                         |                           |           |                                                                  | Min                   | Тур    | Max                      | 1   |  |  |

| I <sub>cc</sub>         | Power Supply Current      | LMX2306   | V <sub>CC</sub> = 2.3V to 5.5 V                                  |                       | 1.7    | 3.5                      | mA  |  |  |

|                         |                           | LMX2316   | V <sub>CC</sub> = 2.3V to 5.5V                                   |                       | 2.5    | 5.0                      | mA  |  |  |

|                         |                           | LMX2326   | $V_{CC} = 2.3V \text{ to } 5.5V$                                 |                       | 4.7    | 7.0                      | mA  |  |  |

| I <sub>CC-PWDN</sub>    | Powerdown Current         |           | V <sub>CC</sub> = 3.0V                                           |                       | 1      |                          | μΑ  |  |  |

| f <sub>IN</sub>         | RF Input Operating        | LMX2306   | V <sub>CC</sub> = 2.3V to 5.5V                                   | 25                    |        | 550                      | MHz |  |  |

|                         | Frequency                 | LMX2316   | V <sub>CC</sub> = 2.3V to 5.5V                                   | 0.1                   |        | 1.2                      | GHz |  |  |

|                         |                           | LMX2326   | V <sub>CC</sub> = 2.3V to 5.5V                                   | 0.1                   |        | 2.1                      | GHz |  |  |

|                         |                           |           | V <sub>CC</sub> = 3.0V to 5.5V                                   | 0.1                   |        | 2.8                      | GHz |  |  |

| f <sub>osc</sub>        | Maximum Oscillator Freque | ency      | V <sub>CC</sub> = 2.3V to 5.5V                                   | 5                     |        | 40                       | MHz |  |  |

|                         |                           |           | $V_{\rm CC} = 2.7 \text{V to } 5.5 \text{V}$                     | 5                     |        | 100                      | MHz |  |  |

| fφ                      | Maximum Phase Detector    | Frequency |                                                                  |                       |        | 10                       | MHz |  |  |

| Pf <sub>IN</sub>        | RF Input Sensitivity      |           | V <sub>CC</sub> = 2.3V to <3.0V                                  | -15                   |        | +0                       | dBm |  |  |

|                         |                           |           | V <sub>CC</sub> = 3.0V to 5.5V                                   | -10                   |        | +0                       | dBm |  |  |

| OSC <sub>IN</sub>       | Oscillator Sensitivity    |           |                                                                  | -5                    |        |                          | dBm |  |  |

| V <sub>IH</sub>         | High-Level Input Voltage  |           | (Note 4)                                                         | 0.8 x V <sub>CC</sub> |        |                          | V   |  |  |

| $V_{IL}$                | Low-Level Input Voltage   |           | (Note 4)                                                         |                       |        | 0.2 x<br>V <sub>CC</sub> | V   |  |  |

| I <sub>IH</sub>         | High-Level Input Current  |           | V <sub>IH</sub> = V <sub>CC</sub> = 5.5V (Note 4)                | -1.0                  |        | 1.0                      | μΑ  |  |  |

| I <sub>IL</sub>         | Low-Level Input Current   |           | V <sub>IL</sub> = 0V, V <sub>CC</sub> = 5.5V<br>(Note 4)         | -1.0                  |        | 1.0                      | μA  |  |  |

| I <sub>IH</sub>         | Oscillator Input Current  |           | $V_{IH} = V_{CC} = 5.5V$                                         |                       |        | 100                      | μA  |  |  |

| I <sub>IL</sub>         | Oscillator Input Current  |           | $V_{IL} = 0V, V_{CC} = 5.5V$                                     | -100                  |        |                          | μA  |  |  |

| ICP <sub>o-source</sub> | Charge Pump Output Curr   | ent       | $V_{Do} = V_p/2$ , ICP <sub>o</sub> = LOW (Note 3)               |                       | -250   |                          | μA  |  |  |

| ICP <sub>o-sink</sub>   |                           |           | $V_{Do} = V_p/2$ , ICP <sub>o</sub> = LOW (Note 3)               |                       | 250    |                          | μA  |  |  |

| ICP <sub>o-source</sub> |                           |           | $V_{Do} = V_p/2$ , ICP <sub>o</sub> = HIGH<br>(Note 3)           |                       | -1.0   |                          | mA  |  |  |

| ICP <sub>o-sink</sub>   |                           |           | $V_{CPo} = V_p/2$ , ICP <sub>o</sub> = HIGH (Note 3)             |                       | 1.0    |                          | mA  |  |  |

| ICP <sub>o-Tri</sub>    | Charge Pump TRI-STATE     | Current   | $0.5 \le V_{CPo} \le V_p - 0.5$<br>-40°C < T <sub>A</sub> < 85°C | -2.5                  |        | 2.5                      | nA  |  |  |

+260°C

**Electrical Characteristics** (Continued)  $V_{CC} = 3.0V$ ,  $V_p = 3.0V$ ;  $-40^{\circ}C < T_A < 85^{\circ}C$  except as specified

| Symbol                              | Parameter                        | Conditions                                                       |                       | Values |     | Units |

|-------------------------------------|----------------------------------|------------------------------------------------------------------|-----------------------|--------|-----|-------|

|                                     |                                  |                                                                  | Min                   | Тур    | Max |       |

| ICP <sub>o-sink vs</sub>            | CP Sink vs Source Mismatch       | $V_{CPo} = V_p/2$                                                |                       | 5      |     | %     |

| ICP <sub>o-source</sub>             |                                  | $T_A = 25^{\circ}C$                                              |                       |        |     |       |

| ICP <sub>o</sub> vs V <sub>Do</sub> | CP Current vs Voltage            | $0.5 \le V_{CPo} \le V_{p} - 0.5$                                |                       | 5      |     | %     |

|                                     |                                  | $T_A = 25^{\circ}C$                                              |                       |        |     |       |

| ICP <sub>o</sub> vs T               | CP Current vs Temperature        | $V_{CPo} = V_p/2$                                                |                       | 5      |     | %     |

|                                     |                                  | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < 85^{\circ}\text{C}$ |                       |        |     |       |

| V <sub>OH</sub>                     | High-Level Output Voltage        | I <sub>OH</sub> = -500 μA                                        | V <sub>CC</sub> - 0.4 |        |     | V     |

| V <sub>OL</sub>                     | Low-Level Output Voltage         | I <sub>OL</sub> = 500 μA                                         |                       |        | 0.4 | V     |

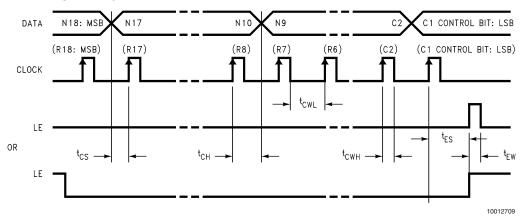

| t <sub>CS</sub>                     | Data to Clock Set Up Time        | See Data Input Timing                                            | 50                    |        |     | ns    |

| t <sub>CH</sub>                     | Data to Clock Hold Time          | See Data Input Timing                                            | 10                    |        |     | ns    |

| t <sub>CWH</sub>                    | Clock Pulse Width High           | See Data Input Timing                                            | 50                    |        |     | ns    |

| t <sub>CWL</sub>                    | Clock Pulse Width Low            | See Data Input Timing                                            | 50                    |        |     | ns    |

| t <sub>ES</sub>                     | Clock to Load Enable Set Up Time | See Data Input Timing                                            | 50                    |        |     | ns    |

| t <sub>EW</sub>                     | Load Enable Pulse Width          | See Data Input Timing                                            | 50                    |        |     | ns    |

Note 3: See PROGRAMMABLE MODES for ICPo description

Note 4: Except  $f_{\text{IN}}$  and  $\text{OSC}_{\text{IN}}$ .

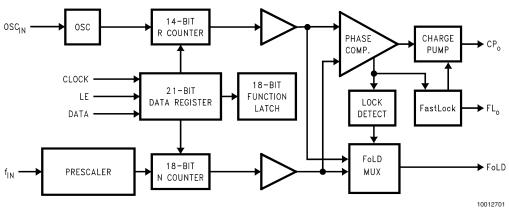

### **Charge Pump Current Specification Definitions**

I1 = Charge Pump Sink Current at  $VCP_0 = V_P - \Delta V$

$I2 = Charge Pump Sink Current at VCP_0 = V_P/2$

I3 = Charge Pump Sink Current at  $VCP_0 = \Delta V$

I4 = Charge Pump Source Current at  $VCP_0 = V_P - \Delta V$

I5 = Charge Pump Source Current at VCP<sub>o</sub> = V<sub>P</sub>/2

I6 = Charge Pump Source Current at  $VCP_0 = \Delta V$

$\Delta V = Voltage$  offset from the positive and negative rails. Dependent on the VCO tuning range relative to  $V_{CC}$  and GND. Typical values are between 0.5V and 1.0V.

### Charge Pump Output Current Magnitude Variation Vs Charge Pump Output Voltage

$$ICP_{o} \text{ Vs VCP}_{o} = \frac{\frac{1}{2}(|11| - |13|)}{\frac{1}{2}(|11| + |13|)} \times 100\%$$

$$= \frac{\frac{1}{2}(|14| - |16|)}{\frac{1}{2}(|14| + |16|)} \times 100\%$$

### Charge Pump Output Current Sink Vs Charge Pump Output Current Source Mismatch

ICP<sub>o</sub> SINK Vs ICP<sub>o</sub> SOURCE =

$$\frac{||12| - |15|}{\frac{1}{2}(||12| + ||15|)} \times 100\%$$

### **Charge Pump Output Current Magnitude Variation Vs Temperature**

ICP<sub>o</sub> Vs T<sub>A</sub> =

$$\frac{|I_2|\Big|_{T_A} - |I_2|\Big|_{T_A = 25^{\circ}C}}{|I_2|\Big|_{T_A = 25^{\circ}C}} \times 100\%$$

$$= \frac{|I_5|\Big|_{T_A} - |I_5|\Big|_{T_A = 25^{\circ}C}}{|I_5|\Big|_{T_A = 25^{\circ}C}} \times 100\%$$

#### RF Sensitivity Test Block Diagram 13 dB ATTN LMX23X6 Evaluation Board 100p 0 $RF~50\,\Omega$ CLOCK Parallel Port DATA SMHU 835.8011.52 $f_{IN}$ 100p PC LE Signal Generator $v_{\rm CC}$ $0.01\mu$ $V_{P}$ FoLD 10 MHz 0 dBm OSCin HP5385A IN 12k 51 HP8657 Signal Frequency Counter Generator PreAmp PCB 39k 100p 100p

2.3V **←►** 5.0V

10012715

Note 5: N=10,000 R=50 P=32

Note 6: Sensitivity limit is reached when the error of the divided RF output, FoLD, is greater than or equal to 1 Hz.

### 1.0 Functional Description

The simplified block diagram below shows the 21-bit data register, a 14-bit R Counter, an 18-bit N Counter, and a 18-bit Function Latch (intermediate latches are not shown). The data stream is shifted (on the rising edge of LE) into the DATA input, MSB first. The last two bits are the Control Bits. The DATA is transferred into the counters as follows:

| Cor | ntrol | DATA Location  |  |  |  |  |

|-----|-------|----------------|--|--|--|--|

| C1  | C2    |                |  |  |  |  |

| 0   | 0     | R Counter      |  |  |  |  |

| 1   | 0     | N Counter      |  |  |  |  |

| 0   | 1     | Function Latch |  |  |  |  |

| 1   | 1     | Initialization |  |  |  |  |

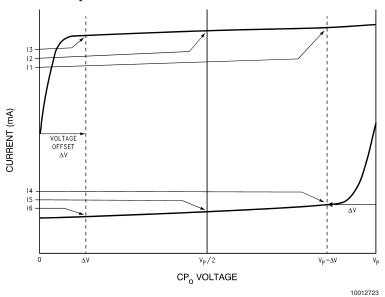

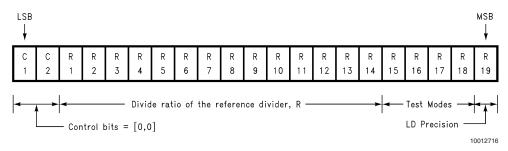

### 1.1 PROGRAMMABLEREFERENCE DIVIDER

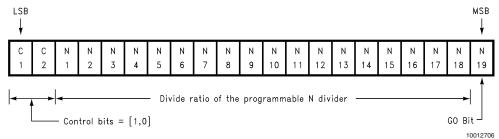

If the Control Bits are  $[C_1, C_2] = [0,0]$ , data is transferred from the 21-bit shift register into a latch that sets the 14-bit R Counter. The 4 bits R15–R18 are for test modes, and should be set to 0 for normal use. The LD precision bit, R19, is described in the LOCK DETECT OUTPUT CHARACTERISTICS section. Serial data format is shown below.

Note: R15 to R18 are test modes and should be zero for normal operation.

Data is shifted in MSB first.

#### 1.1.1 14-bit Programmable Reference Divider Ratio (R Counter)

| Divide | R  | R  | R  | R  | R  | R | R | R | R | R | R | R | R | R |

|--------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|

| Ratio  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 3      | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 4      | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| •      | •  | •  | •  | •  | •  | • | • | • | • | • | • | • | • | • |

| 16383  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Notes: Divide ratios less than 3 are prohibited.

Divide ratio: 3 to 16383

R1 to R14: These bits select the divide ratio of the programmable reference divider.

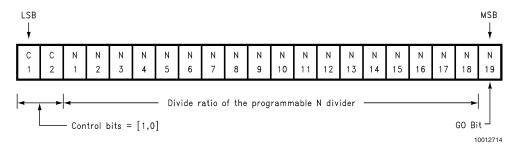

#### 1.2 PROGRAMMABLE DIVIDER (N COUNTER)

The N counter consists of the 5-bit swallow counter (A counter) and the 13-bit programmable counter (B counter). If the Control Bits are  $[C_1, C_2] = [1,0]$ , data is transferred from the 21-bit shift register into a 5-bit latch (which sets the Swallow (A) Counter), a 13-bit latch (which sets the 13-bit programmable (B) Counter), and the GO bit (See Section 1.3.4 FastLock MODES section) MSB first. For the LMX2306 the maximum N value is 65535 and the minimum N value is 56. For the LMX2316/26, the maximum N value is 262143 and the minimum N value is 992. Serial data format is shown below.

Note: Data is shifted in MSB first.

#### 1.2.1 5-bit Swallow Counter Divide Ratio (A Counter)

#### LMX2316/26

| Divide | N | N | N | N | N |

|--------|---|---|---|---|---|

| Ratio  | 5 | 4 | 3 | 2 | 1 |

| 0      | 0 | 0 | 0 | 0 | 0 |

| 1      | 0 | 0 | 0 | 0 | 1 |

| •      | • | • | • | • | • |

| 31     | 1 | 1 | 1 | 1 | 1 |

Note: Divide ratio: 0 to 31

$\mathsf{B} \ge \mathsf{A}$

| Divide | N | N | N | N | N |

|--------|---|---|---|---|---|

| Ratio  | 5 | 4 | 3 | 2 | 1 |

| 1      | Х | Х | 0 | 0 | 1 |

| •      | • | • | • | • | • |

| 7      | Х | Х | 1 | 1 | 1 |

Note: Divide ratio: 0 to 7

$B \ge A$

X denotes a Don't Care condition

### LMX2306

|   | ivide | N | N | N | N | N |

|---|-------|---|---|---|---|---|

| F | Ratio | 5 | 4 | 3 | 2 | 1 |

|   | 0     | Х | Х | 0 | 0 | 0 |

### 1.2.2 13-Bit Programmable Counter Divide Ratio (B Counter)

| Divide | N  | N  | N  | N  | N  | N  | N  | N  | N  | N | N | N | N |

|--------|----|----|----|----|----|----|----|----|----|---|---|---|---|

| Ratio  | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 |

| 3      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 1 | 1 |

| 4      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 1 | 0 | 0 |

| •      | •  | •  | •  | •  | •  | •  | •  | •  | •  | • | • | • | • |

| 8191   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 |

Divide ratio: 3 to 8191 (Divide ratios less than 3 are prohibited) B≥A

### 1.2.3 Pulse Swallow Function

fvco = [(P x B) + A] x fosc/R

$f_{vco}$ : Output frequency of external voltage controlled oscillator (VCO)

B: Preset divide ratio of binary 13-bit programmable counter (3 to 8191)

A: Preset divide ratio of binary 5-bit swallow counter ( $0 \le A \le 31$ ;  $A \le B$  for LMX2316/26) or ( $0 \le A \le 7$ ,  $A \le B$  for LMX2306)

fosc: Output frequency of the external reference frequency oscillator

R: Preset divide ratio of binary 14-bit programmable reference counter (3 to 16383)

P: Preset modulus of dual modulus prescaler for the LMX2306; P = 8 for the LMX2316/26; P = 32

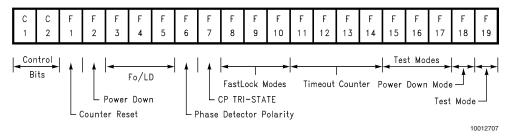

#### 1.3 FUNCTION AND INITIALIZATION LATCHES

Both the function and initialization latches write to the same registers. (See Section 2.1 DEVICE PROGRAMMING AFTER FIRST APPLYING  $V_{\rm CC}$  section for initialization latch description.)

### **TABLE 1. Programmable Modes**

| C1   | C2  | F1      |            | F2      | F   | 3–5     | F6       |       | F7        |     | F8       |

|------|-----|---------|------------|---------|-----|---------|----------|-------|-----------|-----|----------|

| 0    | 1   | COUNTER | POWER DOWN |         | F   | oLD     | PD       |       | CP        |     | FASTLOCK |

|      |     | RESET   |            |         | CON | NTROL   | POLARITY |       | TRI-STATE |     | ENABLE   |

| F    | 9   | F10     |            | F11-14  |     | F15-F17 |          |       | F18       | F19 |          |

| FAS  | ST- | TIMEOUT |            | TIMEOUT |     | TEST    |          | POWER |           | TES | ST .     |

| LOCK |     | COUNTER |            | COUNTER |     | MODES   |          | DOWN  |           | MO  | DF       |

#### **TABLE 2. Mode Select Truth Table**

VALUE

| REGISTER<br>LEVEL | COUNTER<br>RESET | POWER<br>DOWN | PHASE<br>DETECTOR<br>POLARITY | CP<br>TRI-STATE |

|-------------------|------------------|---------------|-------------------------------|-----------------|

| 0                 | RESET            | POWERED       | NEGATIVE                      | NORMAL          |

|                   | DISABLED         | UP            |                               | OPERATION       |

| 1                 | RESET            | POWERED       | POSITIVE                      | TRI-STATE       |

|                   | ENABELED         | DOWN          |                               |                 |

#### **Function Description**

CONTROL

**F1.** The **Counter Reset** enable mode bit F1, when activated, allows the reset of both N and R counters. Upon powering up, the F1 bit needs to be disabled, then the N counter resumes counting in "close" alignment with the R counter. (The maximum error is one prescalar cycle).

F2. Refer to Section 1.3.1 POWERDOWN OPERATION section.

**ENABLE**

F3-5. Controls output of FoLD pin. See FoLD truth table. See Table 4.

**F6. Phase Detector Polarity.** Depending upon VCO characteristics, F6 bit should be set accordingly. When VCO characteristics are positive F6 should be set HIGH; When VCO characteristics are negative F6 should be set LOW

F7. Charge Pump TRI-STATE is set using bit F7. For normal operation this bit is set to zero.

**F8.** When the **FastLock Enable** bit is set the part is forced into one of the four FastLock modes. See description in *Table 5*, FastLock Decoding.

**F9.** The **FastLock Control** bit determines the mode of operation when in FastLock (F8 = 1). When not in FastLock mode,  $FL_o$  can be used as a general purpose output controlled by this bit. For F9 = 1,  $FL_o$  is HIGH and for F9 = 0,  $FL_o$  is LOW. See *Table 5* for truth table.

F10. Timeout Counter Enable bit is set to 1 to enable the timeout counter. See Table 5 for truth table.

F11-14. FastLock Timeout Counter is set using bits F11-14. Table 6 for counter values.

F15-17. Function bits F15-F17 are for Test Modes, and should be set to 0 for normal use.

F18. Refer to Section 1.3.1 POWERDOWN OPERATION section.

F19. Function bit F19 is for a Test Mode, and should be set to 0 for normal use.

MODE

#### 1.3.1 Powerdown Operation

Bits F[2] and F[18] provide programmable powerdown modes when the CE pin is HIGH. When CE is LOW, the part is always immediately disabled regardless of powerdown bit status. Refer to *Table 3*.

Synchronous and asynchronous powerdown modes are both available by MICROWIRE selection. Synchronous powerdown occurs if the F[18] bit (Powerdown Mode) is HIGH when F[2] bit (Powerdown) becomes HIGH. Asynchronous powerdown occurs if the F[18] bit is LOW when its F[2] bit becomes HIGH.

In the synchronous powerdown mode (F[18] = HIGH), the powerdown function is gated by the charge pump to prevent unwanted frequency jumps. Once the powerdown program bit F[2] is loaded, the part will go into powerdown mode after the first successive charge pump event.

In the asynchronous powerdown mode (F[18] = LOW), the device powers down immediately after latching LOW data into bit F[2]. The device returns to an actively powered up condition in either synchronous or asynchronous mode immediately upon LE latching LOW data into bit F[2].

Activation of a powerdown condition in either synchronous or asynchronous mode including CE pin activated powerdown has the following effects:

- · Removes all active DC current paths.

- · Forces the R, N, and timeout counters to their load state conditions.

- · Will TRI-STATE the charge pump.

- · Resets the digital lock detect circuitry.

- Debiases the f<sub>IN</sub> input to a high impedance state.

- · Disables the oscillator input buffer circuitry.

- The MICROWIRE control register remains active and capable of loading the data.

| <b>TABLE</b> | 3. | Power | Down | Truth | <b>Table</b> |

|--------------|----|-------|------|-------|--------------|

|--------------|----|-------|------|-------|--------------|

| CE(Pin 10) | F[2] | F[18] | Mode                    |

|------------|------|-------|-------------------------|

| LOW        | X    | X     | Asynchronous Power Down |

| HIGH       | 0    | X     | Normal Operation        |

| HIGH       | 1    | 0     | Asynchronous Power Down |

| HIGH       | 1    | 1     | Synchronous Power Down  |

TABLE 4. The Fo/LD (pin 14) Output Truth Table

| F[3] | F[4] | F[5] | Fo/LD Output State                                             |  |  |

|------|------|------|----------------------------------------------------------------|--|--|

| 0    | 0    | 0    | TRI-STATE                                                      |  |  |

| 0    | 0    | 1    | R Divider Output (fr)                                          |  |  |

| 0    | 1    | 0    | N Divider Output (fp)                                          |  |  |

| 0    | 1    | 1    | Serial Data Output                                             |  |  |

| 1    | 0    | 0    | Digital Lock Detect (See 1.3.2 LOCK DETECT OUTPUT Section)     |  |  |

| 1    | 0    | 1    | n Channel Open Drain Lock Detect (See 1.3.2 LOCK DETECT OUTPUT |  |  |

|      |      |      | Section)                                                       |  |  |

| 1    | 1    | 0    | Active HIGH                                                    |  |  |

| 1    | 1    | 1    | Active LOW                                                     |  |  |

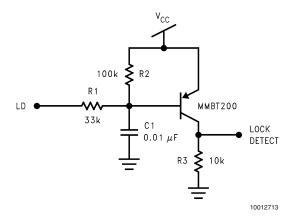

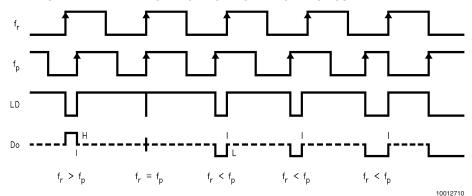

#### 1.3.2 Lock Detect Output Characteristics

Output provided to indicate when the VCO frequency is in "lock." When the loop is locked and the open drain lock detect mode is selected, the pin's output is HIGH, with narrow pulses LOW. When digital lock detect is selected, the output will be HIGH when the absolute phase error is < 15 ns for three or five consecutive phase frequency detector reference cycles, depending on the value of R[19]. Once lock is detected the output stays HIGH unless the absolute phase error exceeds 30 ns for a single reference cycle. Setting the charge pump to TRI-STATE or power down (bits F2, F18) will reset the digital lock detect to the unlocked state. The LD precision bit, R[19], will select five consecutive reference cycles, instead of three, for entering the locked state when R[19] = HIGH.

FIGURE 1. Typical Lock Detect Circuit

#### 1.3.3 Lock Detect Filter Calculation

The component values for the open drain lock detect filter can be determined after assessing the qualifications for an in-lock condition. The in-lock condition can be specified as being a particular number (N) of consecutive reference cycles or duration (D) wherein the phase detector phase error is some factor less than the reference period. In an example where the phase detector reference period is 10 kHz, one might select the threshold for in-lock as occurring when 5 consecutive phase comparisons have elapsed where the phase errors are a 1000 times shorter than the reference period (100 ns). Here, N = 5 and F = 1000.

For the lock detect filter shown in *Figure 1*, when used in conjunction with a open drain (active sink only) lock detect output, the resistor value for R2 would be chosen to be a factor of F \* R1. Thus, if resistor R1 were pulled low for only 1/1000th of the reference cycle period, its "effective" resistance would be on par with R2. The two resistors for that duty cycle condition on average appear to be two 1000x R1 resistors connected across the supply voltage with their common node voltage (Vc) at  $V_{\rm CC}/2$ . Phase errors larger than 1/1000th of the reference cycle period would drag the average voltage of node Vc below  $V_{\rm CC}/2$  indicating an out-of-lock status. If the time constant of R2 \* C1 is now calculated to be N \* the reference period (500 µs), then the voltage of node Vc would fall below  $V_{\rm CC}/2$  only after 5 consecutive phase errors whose average pulse width was greater than 100 ns.

#### 1.3.4 FastLock Modes

FastLock enables the designer to achieve both fast frequency transitions and good phase noise performance by dynamically changing the PLL loop bandwidth. The FastLock modes allow wide band PLL fast locking with seemless transition to a low phase noise narrow band PLL. Consistent gain and phase margins are maintained by simultaneously changing charge pump current magnitude, counter values, and loop filter damping resistor. The four FastLock modes in *Table 5* are similar to the technique used in National Semiconductor's LMX 233X series Dual Phase Locked Loops and are selected by F9, F10, and N19 when F8 is HIGH. Modes 1 and 2 change loop bandwidth by a factor of two while modes 3 and 4 change the loop bandwidth by a factor of 4. Modes 1 and 2 increase charge pump magnitude by a factor of 4 and should use R2'=R2 for consistent gain and phase margin. Modes 3 and 4 increase charge pump magnitude and decrease the counter values by a factor of 4. R2' =  $\frac{1}{3}$  R2 should be used for consistent stability margin in modes 3 and 4. When F8 is LOW, the FastLock modes are disabled, F9 controls only the FL<sub>o</sub> output level (FL<sub>o</sub> = F9), and N19 determines the charge pump current magnitude (N19=LOW $\rightarrow$ ICP<sub>o</sub> = 250  $\mu$ A, N19=HIGH $\rightarrow$ ICP<sub>o</sub> = 1 mA).

**TABLE 5. FastLock Decoding**

| FastLock Status  | F[8] | F[9] | F[10] | <b>N[19]</b><br>(Note 7) | FastLock State                    |

|------------------|------|------|-------|--------------------------|-----------------------------------|

| FastLock Mode #1 | 1    | 0    | 0     | 1 (Note 7)               | No Timeout Counter - 1X Divider   |

| FastLock Mode #2 | 1    | 0    | 1     | 1                        | Timeout Counter - 1X Divider      |

| FastLock Mode #3 | 1    | 1    | 0     | 1 (Note 7)               | No Timeout Counter - 1/4X Divider |

| FastLock Mode #4 | 1    | 1    | 1     | 1                        | Timeout Counter - 1/4X Divider    |

**Note 7:** When the GO bit N[19] is set to one, the part is forced into the high gain mode. When the timeout counter is activated, termination of the counter cycle resets the GO bit to 0. If the timeout counter is not activated, N[19] must be reprogrammed to zero in order to remove the high gain state. See below for descriptions of each individual FastLock mode.

There are two techniques of switching in and out of FastLock. To program the device into any of the FastLock modes, the GO bit N[19] must be set to one to begin FastLock operation. In the first approach, the timeout counter can be used (FastLock 2 and 4) to stay in FastLock mode for a programmable number of phase detector reference cycles (up to 63) and then reset the GO bit automatically. In the second approach (FastLock 1 and 3) without the timeout counter, the PLL will remain in FastLock mode until the user resets the GO bit via the MICROWIRE serial bus. Once the GO bit is set to zero by the timeout counter or by MICROWIRE, the PLL will then return to normal operation. This transition does not effect the charge on the loop filter capacitors and is enacted synchronous with the charge pump output. This creates a nearly seamless transition between FastLock and standard mode.

- FastLock Mode 1 In this mode, the output level of the  $FL_o$  is programmed in a low state while the  $ICP_o$  is in the 4x state. The device remains in this state until a command is received, resetting the N[19] bit to zero. Programming N[19] to zero will return the device to normal operation\*., i.e.,  $ICP_o = 1x$  and  $FL_o$  returned to TRI-STATE.

- FastLock Mode 2 Identical to mode 1, except the switching of the device out of FastLock is controlled by the Timeout counter.

The device will remain in FastLock until the timeout counter has counted down the appropriate number of phase detector cycles, at which time the PLL returns to normal operation\*.

- FastLock Mode 3 This mode is similar to mode 1 in that the output level of the FL<sub>o</sub> is low and the ICP<sub>o</sub> is switched to the 4x state. Additionally, the R and N divide ratios are reduced by one fourth during the transient, resulting in a 16x improved gain. As in mode 1, the device remains in this state until a MICROWIRE command is received, resetting the N[19] bit to zero and returning the device to normal operation\*.

- FastLock Mode 4 Identical to mode 3, except the switching of the device out of FastLock is controlled by the Timeout counter.

The device will remain in FastLock until the timeout counter has counted down the appropriate number of phase detector cycles, at which time the PLL returns to normal operation\*.

\*Normal Operation FastLock Normal Operation is defined as the device being in low current mode and standard divider values.

TABLE 6. FastLock Timeout Counter Value Programming

| Timeout             | 3 | 7 | 11 | 15 | 19 | 23 | 27 | 31 | 35 | • | 59 | 63 |

|---------------------|---|---|----|----|----|----|----|----|----|---|----|----|

| (# PD Cycles) (Note |   |   |    |    |    |    |    |    |    |   |    |    |

| 8)                  |   |   |    |    |    |    |    |    |    |   |    |    |

| F11                 | 0 | 1 | 0  | 1  | 0  | 1  | 0  | 1  | 0  | • | 0  | 1  |

| (4)                 |   |   |    |    |    |    |    |    |    |   |    |    |

| F12                 | 0 | 0 | 1  | 1  | 0  | 0  | 1  | 1  | 0  | • | 1  | 1  |

| (8)                 |   |   |    |    |    |    |    |    |    |   |    |    |

| F13                 | 0 | 0 | 0  | 0  | 1  | 1  | 1  | 1  | 0  | • | 1  | 1  |

| (16)                |   |   |    |    |    |    |    |    |    |   |    |    |

| F14                 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 1  | • | 1  | 1  |

| (32)                |   |   |    |    |    |    |    |    |    |   |    |    |

Note 8: The timeout counter decrements after each phase detector comparison cycle.

### 1.4 SERIAL DATA INPUT TIMING

Notes: Parenthesis data indicates programmable reference divider data.

Data shifted into register on clock rising edge.

Data is shifted in MSB first.

**TEST CONDITIONS:** The Serial Data Input Timing is tested using a symmetrical waveform around  $V_{CC/2}$ . The test waveform has an edge rate of 0.6V/ns with amplitudes of 1.84V @  $V_{CC}$  = 2.3V and 4.4V @  $V_{CC}$  = 5.5V.

### 1.5 PHASE COMPARATOR AND INTERNAL CHARGE PUMP CHARACTERISTICS

Notes: Phase difference detection range: –2 $\pi$  to +2 $\pi$

The Phase Detector Polarity F[6] = HIGH

The minimum width pump up and pump down current pulses occur at the  $ICP_0$  pin when the loop is locked.

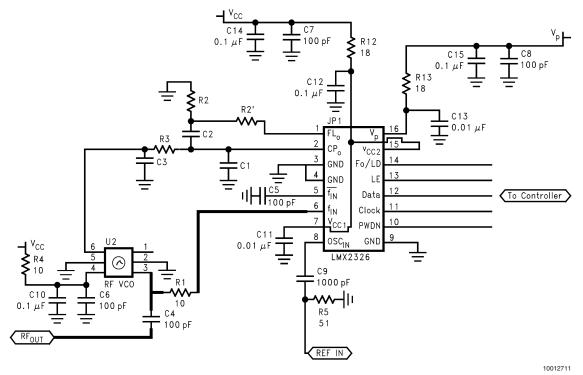

### 1.6 TYPICAL APPLICATION EXAMPLE

### **OPERATIONAL NOTES:**

\*VCO is assumed AC coupled.

\*\*R1 increases impedance so that VCO output power is provided to the load rather than the PLL. Typical values are  $10\Omega$  to  $200\Omega$  depending on the VCO power level.  $f_{\text{IN}}$  RF impedance ranges from  $40\Omega$  to  $100\Omega$ .

\*\*50Ω termination is often used on test boards to allow use of external reference oscillator. For most typical products a CMOS clock is used and no terminating resistor is required. OSC<sub>IN</sub> may be AC or DC coupled. AC coupling is recommended because the input circuit provides its own bias. (See *Figure* below.)

### 2.0 Application Information

## 2.1 DEVICE PROGRAMMING AFTER FIRST APPLYING Voc

Three MICROWIRE programming methods can be used to change the function latch, R counter latch, and N counter latch contents with close phase alignment of R and N counters to minimize lock up time after the cold power up.

#### 2.2 INITIALIZATION SEQUENCE METHOD

Loading the function latch with [C1,C2]=[1,1] immediately followed by an R counter load, then an N counter load, efficiently programs the MICROWIRE. Loading the function latch with [C1,C2]=[1,1] programs the same function latch as a load with [C1,C2]=[0,1] and additionally provides an internal reset pulse described below. This program sequence insures that the counters are at load point when the N counter data is latched in and the part will begin counting in close phase alignment.

The following results from latching the MICROWIRE with an F latch word, [C1, C2] = [1, 1]:

- · The function latch contents are loaded.

- An internal pulse resets the R, N, and timeout counters to load state conditions and will TRI-STATE the charge pump. If the function latch is programmed for the synchronous powerdown case; CE = HIGH, F[2] = HIGH, F[18] = HIGH, this internal pulse triggers powerdown. Refer to Section 1.3.1 POWERDOWN OPERATION section for a synchronous powerdown description. Note that the prescaler bandgap reference and the oscillator input buffer are unaffected by the internal reset pulse, allowing close phase alignment when counting resumes.

- Latching the first N counter data after the initialization word will activate the same internal reset pulse. Successive N counter data loads without an initialization load will not trigger the internal reset pulse.

#### 2.3 CE METHOD

Programming the function latch, R counter latch and N counter latch while the part is being held in a powerdown state by CE allows lowest possible power dissipation. After the MICROWIRE contents have been programmed and the part is enabled, the R and N counter contents will resume counting in close phase alignment. Note that after CE transitions from LOW to HIGH, a duration of 1 µs may be required for the prescaler bandgap voltage and oscillator input buffer bias to reach steady state.

CE can be used to power the part up and down by pin control in order to check for channel activity. The MICROWIRE does not need to be reprogrammed each time the part is enabled and disabled as long as it has been programmed at least once after  $V_{\rm CC}$  was applied.

#### 2.4 COUNTER RESET METHOD

This MICROWIRE programming method consists of a function latch load, [C1, C2] = [0, 1], enabling the counter reset bit, F[1]. The R and N counter latches are then loaded followed by a final function latch load that disables the counter reset. This provides the same close phase alignment as the initialization sequence method with direct control over the internal reset. Note that counter reset holds the counters at load point and will TRI-STATE the charge pump, but does not trigger synchronous powerdown. The counter reset method requires an extra function latch load compared to the initialization sequence method.

#### 2.5 DEVICE PROGRAMMING

When programming the LMX2306, LMX2316, and LMX2326, first determine the frequencies and mode of operation desired. Data register is programmed with a 21-bit data stream shifted into the R counter, N counter, or the F latch. The Functional Description section shows the bits for the R counter, and the corresponding information for the N counter. The FL $_{\rm o}$  programming information is given in the FUNCTION AND INITIALIZATION LATCHES section. Typical numbers for a GSM application example are given. In the example, the RF output is locking at 950 MHz (f $_{\rm vco}$ ) with a 200 kHz channel spacing (f $_{\rm comparison}$ ). The crystal oscillator reference input is 10 MHz (f $_{\rm osc}$ ) and the prescaler value (P) is 32. An example of both methods of FastLock will be shown.

The last two bits (control bits C1 and C2) of each bit stream identify which counter or  $FL_o$  mode will be programmed. For example, to program the R counter, C1 and C2 will be 0,0. Immediately proceeding these two bits is the N, R, or F bits providing the divide ratios and FastLock mode information.

| Contr | ol Bits | DATA Location  |

|-------|---------|----------------|

| C1    | C2      |                |

| 0     | 0       | R Counter      |

| 1     | 0       | N Counter      |

| 0     | 1       | Function Latch |

| 1     | 1       | Initialization |

For example, to load the N counter, the last two bits C1 and C2 must be 10.

Once the control bits have been determined, the frequency information must be determined. To begin, determine the N and R counter values as follows:

$N = f_{vco}/f_{comparison}$

and

$R = f_{osc}/f_{comparison}$

For this example R and N are determined as follows:

R = 10 MHz/200 kHz = 50

and

N = 950 MHz/200 kHz = 4750

### 2.0 Application Information

(Continued)

#### 2.6 N COUNTER

The calculated value of N, and the value of P are now used to determine the values of A and B where A and B are both integer values:

$$N = P * B + A$$

where B is the divisor and A is the remainder. Therefore:

$$B = div (N/P)$$

and

$$A = N - (B * P)$$

For this example, B and A are calculated as follows:

To load the N counter with these values, the programming bit stream would be as follows. The first bit, the GO bit, (MSB) N[19] is used for FastLock operation and will be discussed in the F Latch section. The next 13 bits, (N[18]–N[6]) shifted in, are the B counter value, 0000010010100 $_{\rm b}$  \*. Bits N[5]–N[1] are the A counter and are 01110 $_{\rm b}$  in this example. The final two bits (the control bits) are 1,0 identifying the N counter. In programming the N counter, the value of B must be greater than or equal to A, and the value of B must be greater than or equal to 3.

Note: \*In programming the counter, data is shifted in MSB first.

#### 2.7 R COUNTER

Programming the R counter is done by shifting in the binary value of R calculated previously  $(50_d = 110010_b)$ . The first bit shifted in is R[19] the LD precision bit. The next 4 bits (R[18]–R[15]) shifted in, are used for testing and should

always be loaded with zeros. The R[14]–R[1] bits are used to program the reference divider ratio and should be  $00000000110010_b$  for this example. The final two bits, C[1] and C[2] denote the R counter and should be 0, 0. The resulting bit stream looks as follows:

#### 2.8 F LATCH

To program the device for any of the FastLock modes, C[1] = 0 and C[2] = 1 which direct data to the F latch. The Section 1.3 FUNCTION AND INITIALIZATION LATCH section discusses the 4 modes of FastLock operation. The user must first determine which FastLock mode will be used. When using any of the FastLock modes, the programmer needs to experimentally determine the length of time to stay in high gain mode. This is done by looking at the transient response and determining the time at which the device has settled to

within the appropriate frequency tolerance. FastLock mode should be terminated just prior to "lock" to place the switching phase glitch within the transient settling time. The counter reset mode (F[1] bit) holds both the N and R counters at load point when F[1] = HIGH. Upon setting F[1] = LOW, the N and R counters will resume counting in close phase alignment. Other functions of the F latch such as FoLD output control, Phase detector polarity, and charge pump TRI-STATE are defined in the 1.3 FUNCTION AND INITIALIZATION LATCH section also.

### 2.0 Application Information

(Continued)

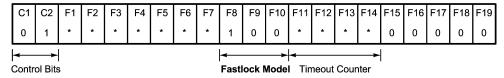

### 2.9 FastLock MODE 1 PROGRAMMING

The F[1]-F[7] bits will be denoted as (\*) and are dependent on the desired modes of the applicable functions. To program the device for mode 1 FastLock, the F[8]-F[10] bits are programmed 100, while the N[19] bit is set to 1. The device will stay in the 4X current mode until another N bit stream is sent with the N[19] bit reset to 0. This gives a bit stream as follows:

10012717

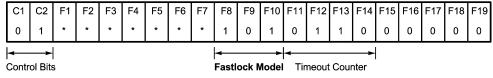

### 2.10 FastLock MODE 2 PROGRAMMING

Again, the F[1]-F[7] bits will be denoted as don't care (\*) but are dependent on the desired modes of the applicable functions. To program the device for mode 2 FastLock, the F[8]-F[10] bits are programmed 101, while the N[19] bit is set to 1. The device will stay in the 4X current mode for the programmed number of phase detector cycles. Bits

F[11]–F[14] program this number of cycles and are shown in *Table 6*. For our example, we will use 27 phase detector cycles, i.e. bits F[11]–F[14] will be  $0110_{\rm b}$ . After 27 phase detector cycles, the N[19] bit returns to zero, bringing the device back to low current mode. The resulting bit stream is as follows:

10012718

FastLock modes 3 and 4 are programmed in the same manner and give the added 4X gain increase as discussed in

Section 1.3.4 FastLock modes.

### Physical Dimensions inches (millimeters) unless otherwise noted В 6.4 (16X 0.42) 3.2 (14X 0.65) GAGE PLANE RECOMMENDED LAND PATTERN 0.25 O.2 CBA ALL LEAD TIPS SEATING PLANE DETAIL A SEE DETAIL A 1.1 MAX (0.9) 0.1±0.05 TYP ALL LEAD TIPS 16X 0.19-0.30 ⊕ 0.13M A BS CS 14X 0.65 DIMENSIONS ARE IN MILLIMETERS DIMENSIONS IN ( ) FOR REFERENCE ONLY MTC16 (Rev D)

16-Lead (0.173" Wide) Thin Shrink Small Outline Package (TM)

Order Number LMX2306TM, LMX2316TM or LMX2326TM

For Tape and Reel (2500 Units Per Reel)

Order Number LMX2306TMX, LMX2316TMXor LMX2326TMX

NS Package Number MTC16

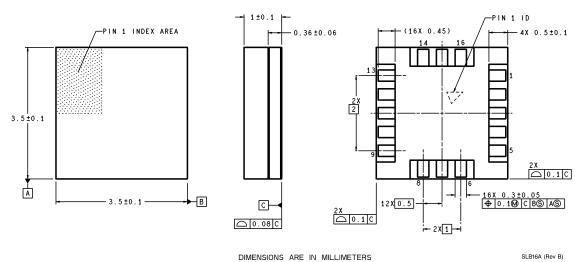

### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

RECOMMENDED LAND PATTERN

1:1 RATIO WITH PACKAGE SOLDER PADS

16-Pin Chip Scale Package (SLB)

Order Number LMX2306SLBX, LM2316SLBX or LM2326SLBX

NS Package Number SLB16A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560